Проектирование электронных изделий включает в себя чертежи принципиальных схем, компоновку печатных плат и монтаж проводов. Из-за недостатка знаний в этой области опыта работы часто возникают различные ошибки, затрудняющие нашу дальнейшую работу, а в тяжелых случаях изготовленные платы вообще не могут быть использованы. Поэтому нам следует стараться изо всех сил совершенствовать свои знания в этой области и избегать всевозможных ошибок.

В этой статье описаны распространенные проблемы сверления при использовании чертежных досок для печатных плат, чтобы избежать наступления на одни и те же ямы в будущем. Бурение делится на три категории: сквозное отверстие, глухое отверстие и заглубленное отверстие. Сквозные отверстия включают вставные отверстия (PTH), отверстия для позиционирования винтов (NPTH), глухие, заглубленные отверстия и сквозные отверстия (VIA), все из которых играют роль многослойной электропроводности. Независимо от типа отверстия, следствием проблемы отсутствия отверстий является то, что всю партию продукции невозможно использовать напрямую. Поэтому правильность проектирования бурения имеет особое значение.

Объяснение ямок и утечек на конструктивной стороне печатных плат

Проблема 1: Слоты для файлов, разработанные Altium, неуместны;

Описание проблемы: Слот отсутствует, и продукт не может быть использован.

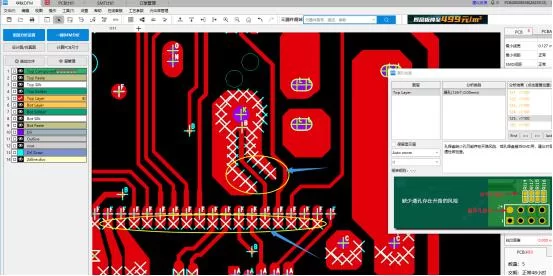

Анализ причин: Инженер-конструктор при изготовлении упаковки пропустил слот для USB-устройства. Когда он обнаружил эту проблему при рисовании платы, он не стал модифицировать корпус, а непосредственно нарисовал прорезь на слое с символом отверстия. Теоретически большой проблемы с этой операцией нет, но в производственном процессе для сверления используется только слой сверления, поэтому можно легко проигнорировать наличие прорезей в других слоях, в результате чего просверливание этой прорези будет пропущено, и изделие невозможно будет использовать. Пожалуйста, смотрите картинку ниже;

Как избежать ям: Каждый уровень файла дизайна печатной платы OEM имеет функцию каждого слоя. Сверла и пазы должны располагаться в слое сверления, и нельзя считать, что конструкция может быть изготовлена.

Вопрос 2: файл, разработанный Altium, с помощью кода отверстия 0 D;

Описание проблемы: Утечка является открытой и непроводящей.

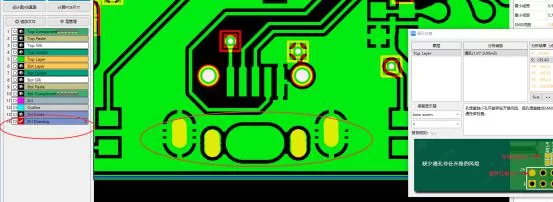

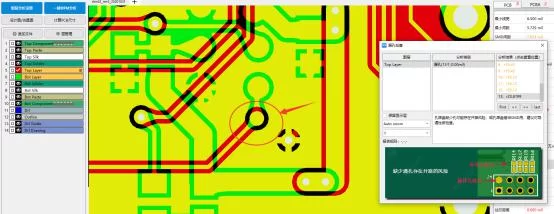

Анализ причин: См. рисунок 1. В файле проекта имеется утечка, и утечка указана во время проверки технологичности DFM. После проверки причины утечки диаметр отверстия в программном обеспечении Altium равен 0, в результате чего в файле проекта дыр нет, см. рисунок 2.

Причина появления утечки в том, что инженер-проектировщик допустил ошибку при сверлении отверстия. Если проблема с этим отверстием для утечки не проверена, найти отверстие для утечки в файле проекта будет сложно. Отверстие для утечки напрямую влияет на электрический сбой, и разработанное изделие невозможно использовать.

Как избежать ям: Проверка технологичности DFM должна проводиться после завершения проектирования принципиальной схемы. Утечки переходных отверстий невозможно обнаружить на производстве и во время проектирования. Проверка технологичности DFM перед производством позволяет избежать этой проблемы.

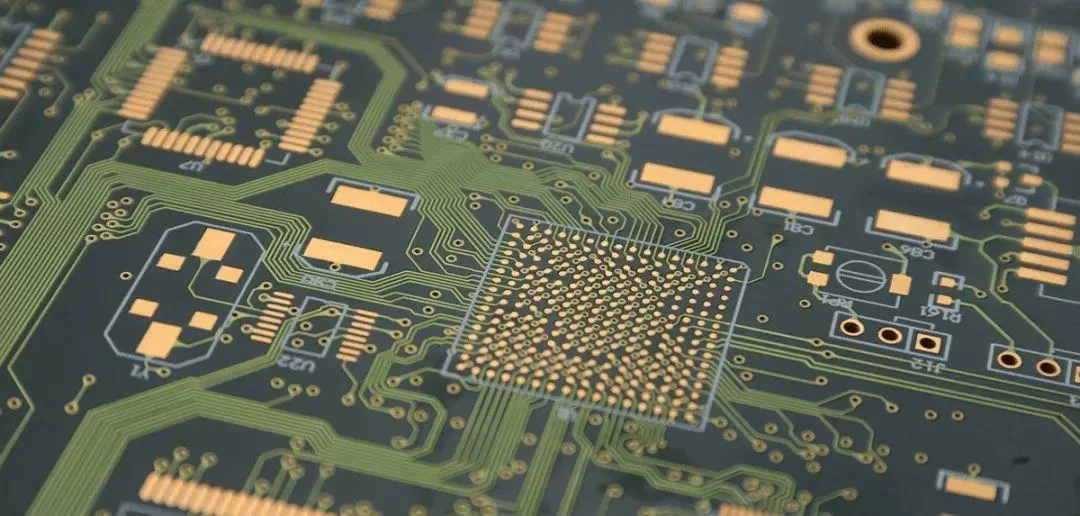

Рисунок 1. Утечка файла дизайна

Рисунок 2. Апертура Altium равна 0.

Вопрос 3: Файловые переходы, разработанные PADS, не могут быть выведены;

Описание проблемы: Утечка является открытой и непроводящей.

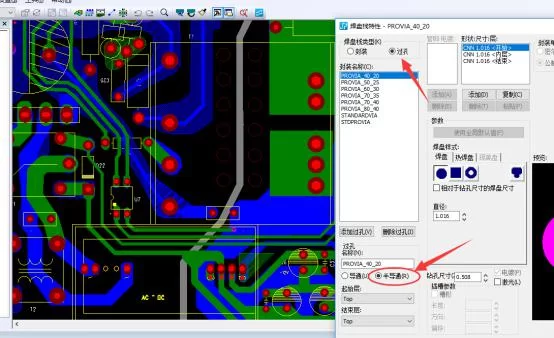

Анализ причин: См. рисунок 1. При проведении испытаний технологичности DFM видно большое количество утечек. После проверки причины проблемы с утечкой одно из переходных отверстий в PADS было спроектировано как полупроводниковое отверстие, в результате чего в файле проекта не отображалось полупроводниковое отверстие, что приводило к утечке, см. рисунок 2.

Двусторонние панели не имеют полупроводниковых отверстий. При проектировании инженеры ошибочно определили сквозные отверстия как полупроводниковые, а выходные полупроводниковые отверстия протекают во время выходного сверления, что приводит к образованию негерметичных отверстий.

Как избежать ям: Такую ошибку не так-то просто обнаружить. После завершения проектирования необходимо провести анализ и проверку технологичности DFM и выявить проблемы перед производством, чтобы избежать проблем с утечками.

Рисунок 1. Утечка файла дизайна

Рис. 2. Двухпанельные переходные отверстия программного обеспечения PADS являются полупроводниковыми.